Wie in allen anderen Bereichen der Elektronik steigen auch besonders in der HF-Technologie die Anforderungen nach Miniaturisierung und schnellen Entwurfszyklen. Entsprechend wichtig ist es, zuverlässige, effiziente Prototyping-Verfahren zu finden, wobei Multilayer-Anwendungen eine besondere Herausforderung dafür darstellen.

Das In-house PCB Prototyping bietet eine Reihe von überzeugenden Vorteilen für die Forschung und Entwicklung im HF-Bereich. Die Ingenieure benötigen vom Design bis zum fertigen Prototyp nur wenige Stunden, können über die Maschinensoftware Designänderungen vornehmen und behalten die volle Benutzerkontrolle über das Prototyping-Verfahren. Bei Multilayer-Anwendungen wird zunächst das Design auf die Oberfläche der Leiterplatte gefräst oder mit Lasertechnik bearbeitet. Dann werden die Substrate miteinander verpresst, gebohrt und schließlich durchkontaktiert, um einen funktionsfähigen Multilayeraufbau zu erhalten. In diesem Beitrag erfahren Sie, wie zuverlässig Multilayerleiterplatten in-house hergestellt werden können.

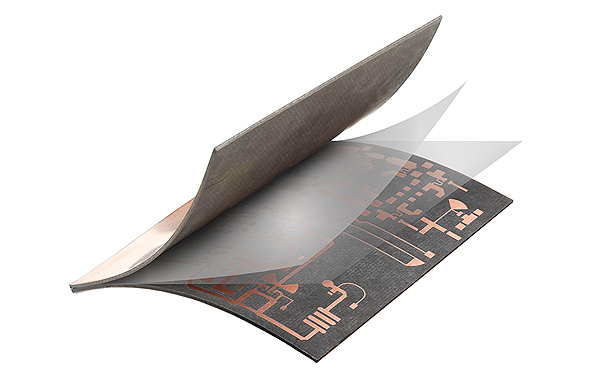

Um die Effektivität der Erstellung einer Multilayer-HF-Platine im eigenen Haus zu messen, wurde ein 4-Lagen-Stack-up verwendet, bestehend aus zwei einseitig verkupferten Außenlagen und einer beidseitig verkupferten Innenlage. Die verwendeten Substrate gehören zu den gängigsten HF-Materialien, die auf dem Markt erhältlich sind. Für die Außenlagen wurde Rogers RT/duroid 5880 NS verwendet, für die Innenlage Rogers 4003C. Beide Materialien lassen sich sowohl mit Fräs- als auch mit Lasertechnik einfach strukturieren. Als Prepreg zwischen den Lagen wurde eine hochwertige thermoplastische Klebefolie, Rogers 3001, verwendet. Diese Folie empfiehlt sich für die Verbindung von Leiterplattenschichten mit einer niedrigen Dielektrizitätskonstante, wie die in dieser Studie verwendeten Rogers-Materialien.

Nach dem Verpressen der Lagen sollte die Klebefolie ihre Klebefähigkeit gegenüber äußeren Einflüssen, z. B. Temperatur und Feuchtigkeit, beibehalten. Um dies zu messen, wurden auf den äußeren Platinenschichten Testschaltungen mit 3 x 70 mm Streifen angelegt, wobei die innere Schicht als freie Kupferfläche verblieb. Mittels Klimaschrank wurde ein Temperaturwechsel erzeugt, der die oben genannten äußeren Einflüsse entsprechend simuliert. Im Zeitraum von 60 Minuten wurde jede Testplatine Temperaturen von 40°C und 125°C ausgesetzt. Jede Platine durchlief zehn Zyklen, wonach ein Streifen der Kupferoberfläche und ein Streifen der freien Oberfläche mit einem Zugversuch auf Haftfestigkeit gemessen wurde. Insgesamt durchliefen beide Testplatinen 50 Zyklen. Der Wert im Zugversuch lag jeweils bei >1N/mm und erreichte damit die vor dem Test festgelegten Richtwerte für die Haftfestigkeit.

Zur Messung der Effektivität der Durchkontaktierungen auf allen vier Seiten der Testleiterplatte wurden sogenannte Daisy-Chain-Strukturen genutzt. Die Daisy Chain umfasst Löcher mit Durchmessern von 0,5 mm, 0,6 mm, 0,7 mm, 0,8 mm und 0,9 mm. Nach dem Bohren der Löcher wurden die Lagen durch den galvanischen Aufbau einer Kupferschicht von jeweils 25 μm verbunden. Mittels Widerstandsmessung wurden für jeden Durchmesser in der Daisy-Chain-Reihe Werte ermittelt Bei jedem Loch wurde ein Widerstand <50 mΩ gemessen, was wiederum die Testziele erfüllte.

Ein 4-Lagen-HF-Stapel, wie er für diese Fallstudie verwendet wurde, kann mit LPKF-Systemen zuverlässig gebondet und beschichtet werden. Das bedeutet, dass Forschungs- und Entwicklungsingenieure die Möglichkeit haben, schnell und effizient Multilayer-HF-Anwendungen im Haus zu erstellen.